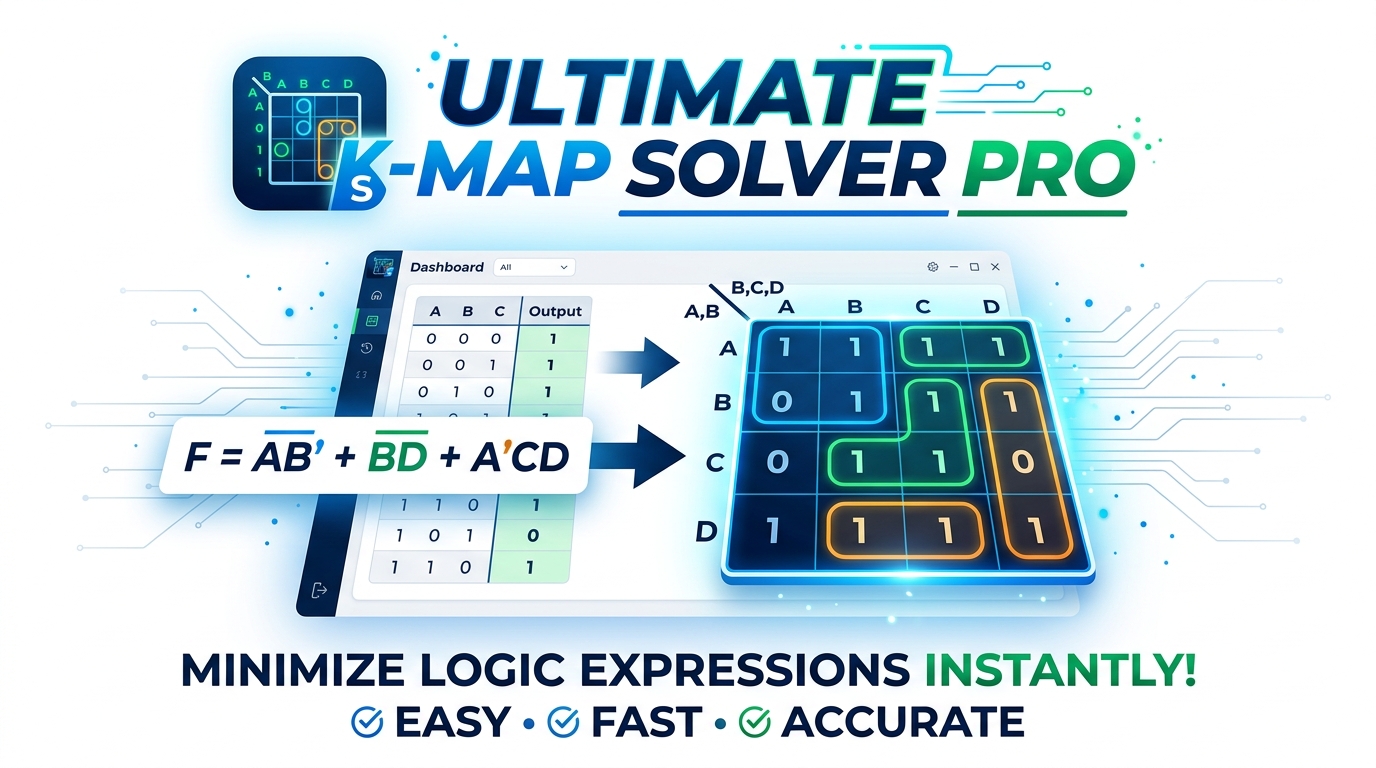

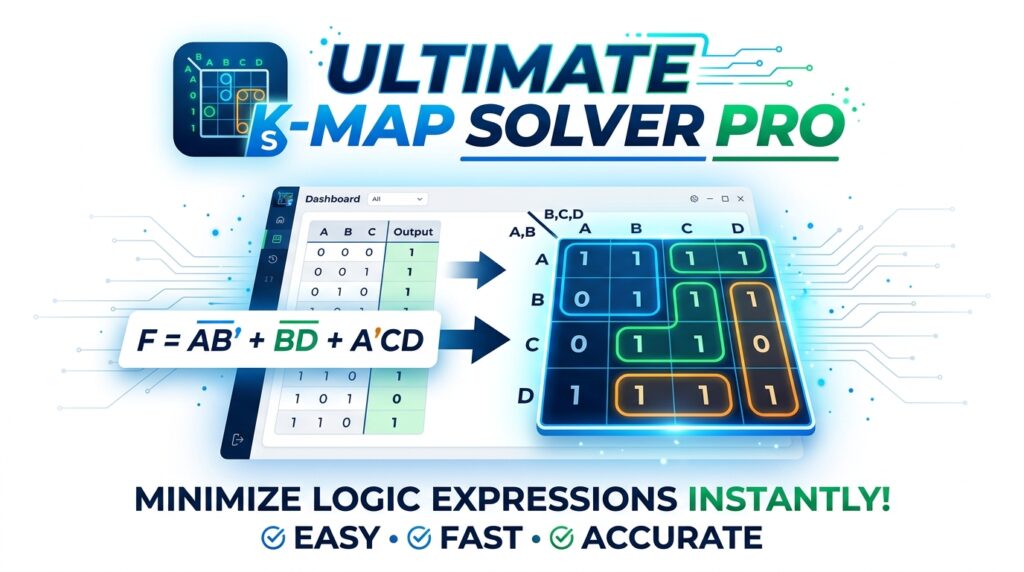

Ultimate K-Map Solver Pro: Karnaugh Map Calculator | 2 to 5 Variable Boolean Minimizer

I100% offline, lightning-fast K-Map solver. Visualize 2 to 5 variable Karnaugh maps, generate optimized Boolean expressions (SOP/POS), and export Verilog HDL code instantly.

Table of Contents

Ultimate K-Map Solver Pro

Elite 2-5 variable logic minimizer with offline visual grouping.

Karnaugh Map Visualizer

🟦 Advanced Minimization Algorithm

Utilizes a highly optimized variant of the Quine-McCluskey method to process 2 to 5 variable boolean expressions instantly directly in your browser.

🟩 Verilog HDL Code Generation

Instantly export synthesizable Verilog HDL code based on your minimized logic, ready for deployment in FPGA or ASIC design workflows.

🟪 Multi-Color Visual Grouping

Interactive Karnaugh map visualizer maps out pairs, quads, octets, and wrap-around edge groups with distinct color coding for deep step-by-step analysis.

How to Generate a Minimized Expression

Configure Variables

Select the number of logic variables (2, 3, 4, or 5) and choose your preferred optimization method (SOP or POS) from the control panel.

Input Truth Table

Click on the ‘F’ column in the truth table to toggle states between True (1), False (0), or Don’t Care (X) conditions for your digital circuit.

Analyze & Export

Click generate to view the interactive K-Map grid, analyze the grouping logic, and copy the final Boolean equation or Verilog code.

🟦 Advanced K-Map Solver: Master Boolean Simplification

Welcome to the #1 Advanced K-Map Solver on Prime Tool Hub. Our Karnaugh Map calculator is engineered for students and professionals in Tier 1 engineering programs. Whether you are dealing with Sum of Products (SOP) or Product of Sums (POS), our visual solver provides instantaneous, high-precision results for up to 4 variables.

✅ No Registration Required | ✅ 100% Offline (Local Browser) | ✅ Easy Print & Export

🟩 Why Use a Karnaugh Map Calculator?

Manual Boolean simplification using theorems is prone to human error. A K-Map Solver uses visual grouping patterns to eliminate redundant variables automatically. This process is essential for:

- 🟧 Hardware Efficiency: Reducing the number of logic gates in a physical circuit.

- 🟧 Digital Design: Converting expressions for FPGA or ASIC programming.

- 🟧 Academic Success: Cross-checking university-level digital logic assignments.

🟩 Understanding SOP vs. POS Minimization

Depending on your circuit design, you may prefer one form over the other:

- 🟨 Sum of Products (SOP): Focuses on the ‘1’ outputs of your truth table. It utilizes AND gates feeding into an OR gate.

- 🟨 Product of Sums (POS): Focuses on the ‘0’ outputs. It is often more efficient for expressions where the output is mostly true.

🟩 Comprehensive K-Map Grouping Rules

To use this tool effectively, remember these core principles of grouping:

- 🟧 Power of 2: Groups must consist of 1, 2, 4, 8, or 16 cells. Groups of 3 or 6 are strictly invalid.

- 🟧 Maximize Group Size: Always look for the largest possible group (e.g., an Octet is better than two Quads).

- 🟧 Wrap-Around Logic: K-Maps are not flat. The left edge touches the right, and the top touches the bottom.

🟩 Frequently Asked Questions (FAQs)

🟥 What are “Don’t Care” (X) conditions?

Don’t care conditions are inputs that do not occur in your specific application. Our solver allows you to use ‘X’ to create larger groups, further simplifying your logic.

🟥 Can I export the Verilog code?

Yes. Once simplified, the tool generates synthesizable Verilog HDL code that can be copied directly into simulators like ModelSim or Vivado.

Experience the most advanced visual K-Map Minimizer for high-speed digital logic design today at Prime Tool Hub! Read Full SEO Article ▼